# **Arithmetic Circuits**

- 1. Adder

- 2. Multiplier

- 3. Arithmetic Logic Unit (ALU)

- 4. HDL for Arithmetic Circuit

### Introduction

- 1. Digital circuits are frequently used for arithmetic operations

- 2. Fundamental arithmetic operations on binary numbers and digital circuits which perform arithmetic operations will be examined.

- 3. HDL will be used to describe arithmetic circuits.

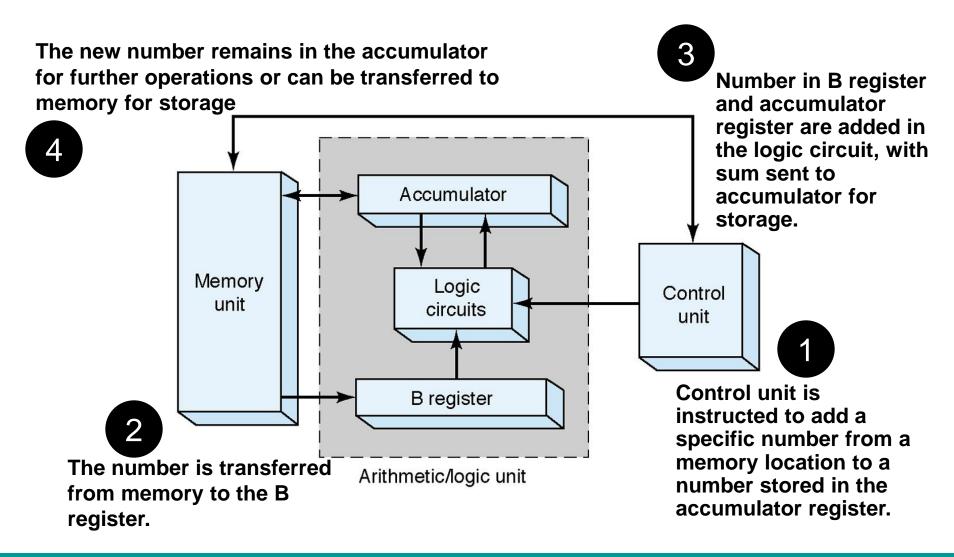

- 4. An arithmetic/logic unit (ALU) accepts data stored in memory and executes arithmetic and logic operations as instructed by the control unit.

### **Arithmetic Circuits**

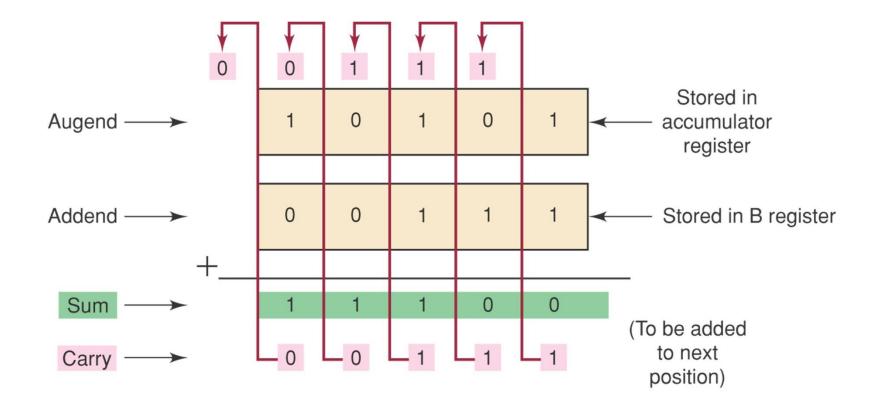

### **Typical binary addition process**

#### **Nurul Hazlina**

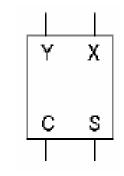

### Half Adder

| Χ | Y | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 |   | 1 |

| 1 | 0 | Õ | 1 |

| 1 | 1 | 1 | 0 |

Half Adder equation

$$C = XY$$

$$S = X'Y + XY'$$

$$= X \oplus Y$$

$\mathcal{C}$

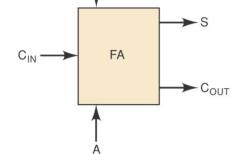

### **Full Adder**

| Augend<br>bit<br>input | Addend<br>bit<br>input | Carry<br>bit<br>input |   | Sum<br>bit<br>output | Carry<br>bit<br>output |

|------------------------|------------------------|-----------------------|---|----------------------|------------------------|

| А                      | В                      | C <sub>IN</sub>       |   | S                    | C <sub>OUT</sub>       |

| 0                      | 0                      | 0                     |   | 0                    | 0                      |

| 0                      | 0                      | 1                     |   | 1                    | 0                      |

| 0                      | 1                      | 0                     |   | 1                    | 0                      |

| 0                      | 1                      | 1                     |   | 0                    | 1                      |

| 1                      | 0                      | 0                     |   | 1                    | 0                      |

| 1                      | 0                      | 1                     |   | 0                    | 1                      |

| 1                      | 1                      | 0                     |   | 0                    | 1                      |

| 1                      | 1                      | 1                     |   | 1                    | 1                      |

|                        | 1 1                    | 1                     | 0 |                      |                        |

|                        | 1                      | 0                     | 1 | 1                    |                        |

|                        | + 1                    | 1                     | 1 | 0                    |                        |

|                        | 1 1                    | 0                     | 0 | 1                    |                        |

$$S = \Sigma m(1,2,4,7)$$

= X'Y'C<sub>in</sub> + X'YC<sub>i</sub>' + XY'C<sub>i</sub>' + XYC<sub>in</sub>

= X'(Y'C<sub>in</sub> + YC<sub>in</sub>') + X(Y'C<sub>in</sub>' + YC<sub>in</sub>)

= X'(Y  $\oplus$  C<sub>in</sub>) + X(Y  $\oplus$  C<sub>in</sub>)'

= X  $\oplus$  Y  $\oplus$  C<sub>in</sub>

$$C_{out} = \Sigma m(3,5,6,7)$$

= X'YC<sub>in</sub> + XY'C<sub>in</sub> + XYC<sub>in</sub>' + XYC<sub>in</sub>

= (X'Y + XY')C<sub>in</sub> + XY(C<sub>in</sub>' + C<sub>in</sub>)

= (X \overline Y)C<sub>in</sub> + XY

# Full-adder-K map, Complete circuitry

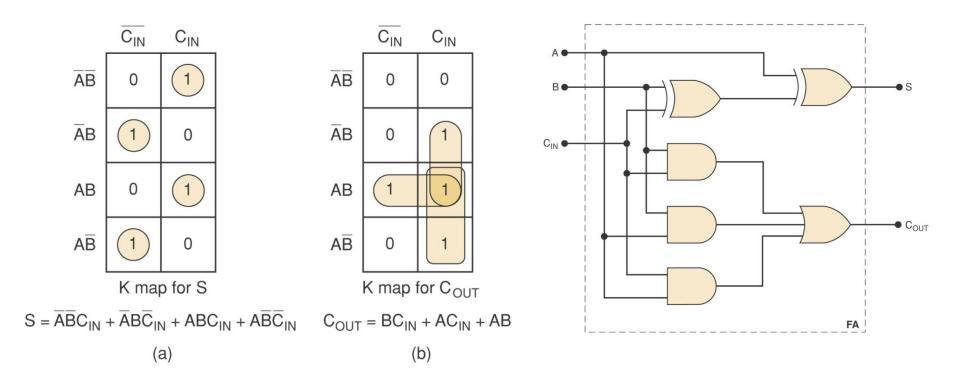

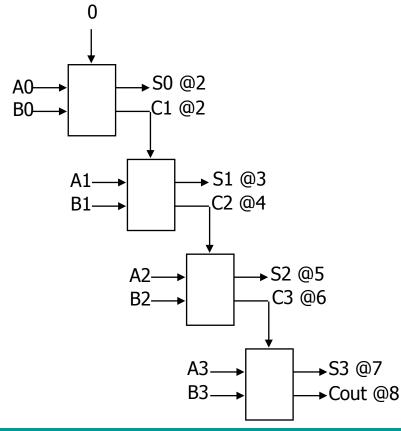

# **Ripple Carry Adder**

- This is called a ripple carry adder, because the inputs A0, B0 and CI "ripple" leftwards until CO and S3 are produced.

- Ripple carry adders are slow!

- There is a very long path from A0, B0 and CI to CO and S3.

- For an *n*-bit ripple carry adder, the longest path has 2*n*+1 gates.

- The longest path in a 64-bit adder would include 129 gates!

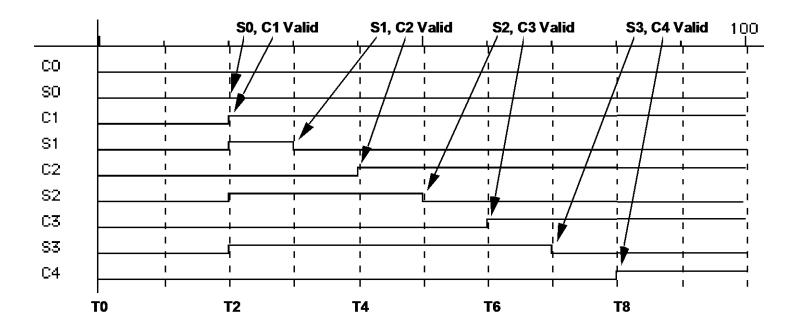

### **Ripple-carry adders**

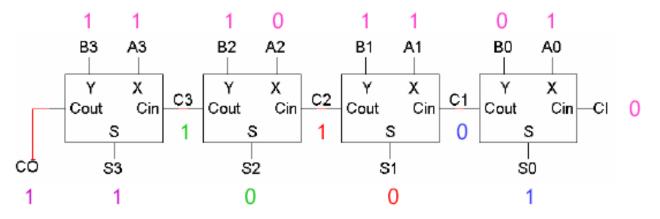

# Ripple-carry adders (cont'd)

- Critical delay

- the propagation of carry from low to high order stages

- 1111 + 0001 is the worst case addition

- carry must propagate through all bits

- Carry look-ahead solves this problem ٠ by calculating the carry signals in advance, based on the input signals.

- It is based on the fact that a carry signal will be generated in two ٠ cases:

(1) when both bits Ai and Bi are 1, or

(2) when one of the two bits is 1 and the carry-in (carry of the previous) stage) is 1.

### **Carry look ahead adder**

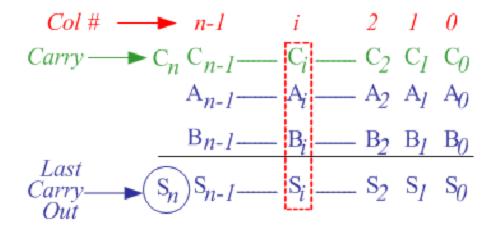

• To understand the carry propagation problem, let's consider the case of adding two n-bit numbers A and B.

### **Carry look ahead adder**

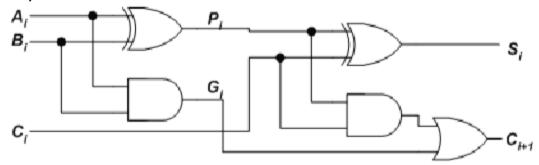

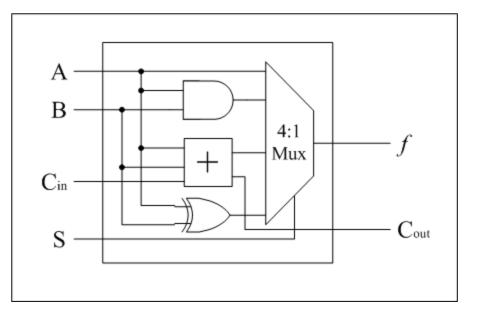

The Figure shows the full adder circuit used to add the operand bits in the ith column; namely Ai & Bi and the carry bit coming from the previous column (Ci).

In this circuit, the 2 internal signals Pi and Gi are given by:

Pi = Ai ⊕ Bi .....(1)

G i = Ai B i.....(2)

The output sum and carry can be defined as :

Si = Pi  $\oplus$  Ci .....(3) C i +1 = G i + Pi C i .....(4)

### **Carry look ahead adder**

- Gi is known as the carry Generate signal since a carry (Ci+1) is generated whenever Gi=1, regardless of the input carry (Ci).

- Pi is known as the carry propagate signal since whenever Pi =1, the input carry is propagated to the output carry, i.e., Ci+1. = Ci (note that whenever Pi =1, Gi =0).

- Computing the values of Pi and Gi only depend on the input operand bits (Ai & Bi) as clear from the Figure and equations.

- Thus, these signals settle to their steady-state value after the propagation through their respective gates.

- Computed values of all the Pi's are valid one XOR-gate delay after the operands A and B are made valid.

- Computed values of all the Gi's are valid one AND-gate delay after the operands A and B are made valid.

### **Carry-lookahead logic**

- Carry generate: Gi = Ai Bi

- must generate carry when A = B = 1

- Carry propagate: Pi = Ai xor Bi

- carry-in will equal carry-out here

- Sum and Cout can be re-expressed in terms of generate/propagate:

- Si = Ai xor Bi xor Ci

- = Pi xor Ci

-

$$Ci+1 = Ai Bi + Ai Ci + Bi Ci$$

=  $Ai Bi + Ci (Ai + Bi)$

=  $Ai Bi + Ci (Ai xor Bi)$

=  $Gi + Ci Pi$

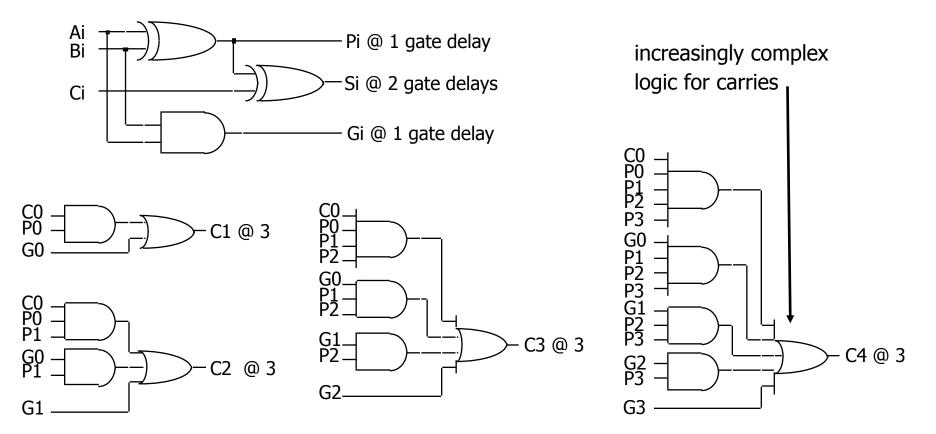

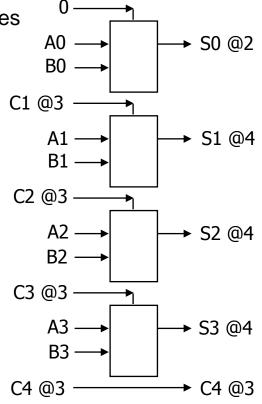

# Carry-lookahead logic (cont'd)

- Re-express the carry logic as follows:

- C1 = G0 + P0 C0

- C2 = G1 + P1 C1 = G1 + P1 G0 + P1 P0 C0

- C3 = G2 + P2 C2 = G2 + P2 G1 + P2 P1 G0 + P2 P1 P0 C0

- C4 = G3 + P3 C3 = G3 + P3 G2 + P3 P2 G1 + P3 P2 P1 G0

+ P3 P2 P1 P0 C0

- Each of the carry equations can be implemented with two-level logic

- all inputs are now directly derived from data inputs and not from intermediate carries

- this allows computation of all sum outputs to proceed in parallel

# Carry-lookahead implementation

Adder with propagate and generate outputs

#### **Electronic System Design**

**Arithmetic Circuits**

### Carry-lookahead implementation (cont'd)

- Carry-lookahead logic generates individual carries

- sums computed much more quickly in parallel

- however, cost of carry logic increases with more stages

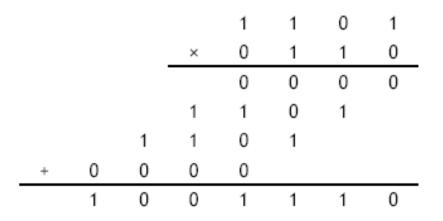

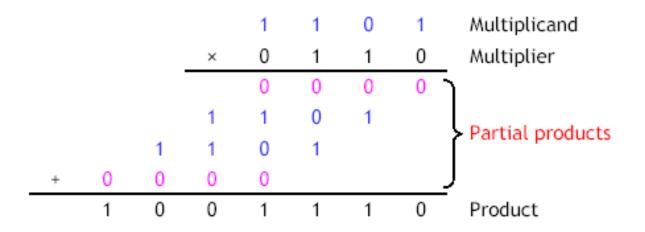

# MULTIPLIER

### Multiplication

- Multiplication can't be that hard! It's just repeated addition, so if we have adders, we should be able to do multiplication also.

- Here's an example of binary multiplication

# **Binary Multiplication**

- Since we always multiply by either 0 or 1, the partial products are always either 0000 or the multiplicand (1101 in this example).

- There are four partial products which are added to form the result.

- We can add them in pairs, using three adders.

- The product can have up to 8 bits, but we can use four-bit adders if we stagger them leftwards, like the partial products themselves.

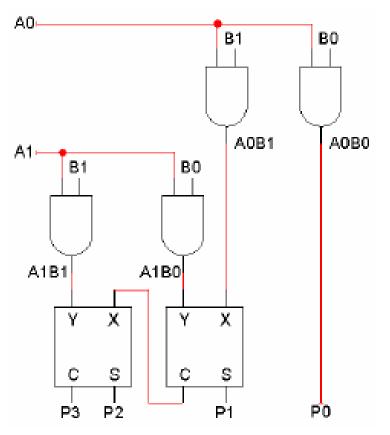

# **2X2 Binary Multiplication**

• Here is an outline of multiplying the two-bit numbers A1A0 and B1B0, to produce the four-bit product P3-P0.

|   |    |      | B1   | В0   |

|---|----|------|------|------|

|   |    |      |      |      |

|   |    | ×    | A1   | A0   |

|   |    |      | A0B1 | A0B0 |

|   |    |      |      |      |

| + |    | A1B1 | A1B0 |      |

|   | D2 | P2   | D1   | P0   |

- The bits of each partial product are computed by multiplying two bits of the input.

- Since two-bit multiplication is the same as the logical AND operation, we can use AND gates to generate the partial products.

### **2X2 Binary Multiplication**

- Here is a circuit that multiplies the two-bit numbers A1A0 and B1B0, resulting in the four-bit product P3-P0.

- For a 2x2 multiplier we can just use two half adders to sum the partial products. In general, though, we'll need full adders.

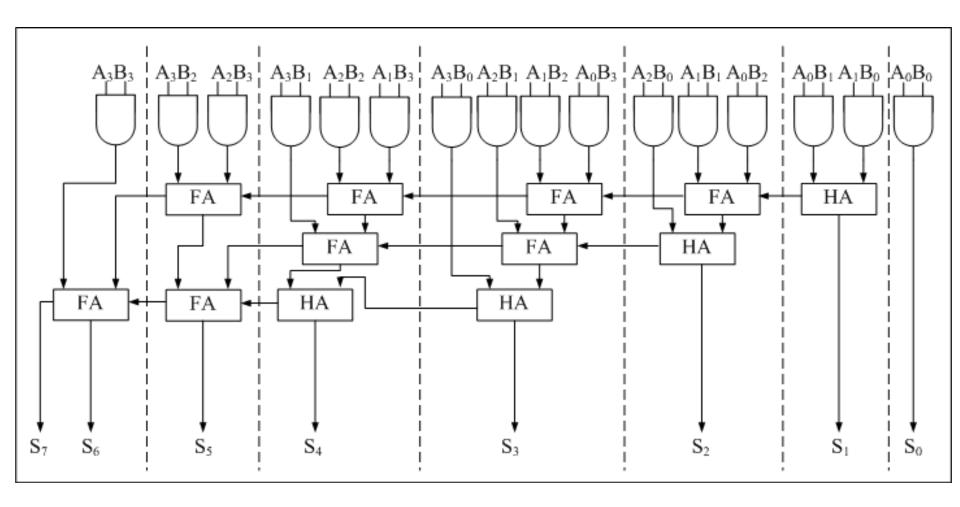

- The diagram on the next page shows how this can be extended to a four-bit multiplier, taking inputs A3-A0 and B3-B0 and outputting the product P7-P0.

#### **Electronic System Design**

**Arithmetic Circuits**

### A 4×4 binary multiplier

# **Complexity of multiplication circuits**

- In general, when multiplying an *m*-bit number by an *n*-bit number:

- There will be *n* partial products, one for each bit of the multiplier.

- This requires *n*-1 adders, each of which can add *m* bits.

- The circuit for 32-bit or 64-bit multiplication would be huge!

# **ARITHMETIC LOGIC UNIT**

# A 1-Bit ALU

| Operation<br>S1 S0 | Function |

|--------------------|----------|

| 0 0                | А        |

| 0 1                | A•B      |

| 1 0                | A + B    |

| 1 1                | A XOR B  |

> The multiplexer selects either

$A, A \bullet B, A + B \text{ or } A XOR B$

depending on whether the value of operation, S is 00, 01, 10 or 11.

> To add an operation, the multiplexer has to be expanded

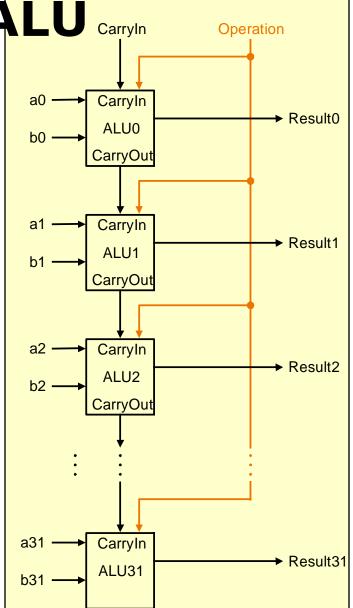

# A 32-Bit ALU

- A full 32-bit ALU can be created by connecting adjacent 1-bit ALU's

- using the Carry in and carry out lines

- The carry out of the least significant bit can ripple all the way through the adder (*ripple carry adder*)

- Ripple carry adders are slow since the carry propagates from a unit to the next sequentially

- Subtraction can be performed by inverting the operand and setting the "CarryIn" input for the whole adder to 1 (i.e. using two's complement)

### A 32-Bit ALU Carryln

- A full 32-bit ALU can be created by connecting adjacent 1-bit ALU's using the Carry in and carry out lines

- 2. The carry out of the least significant bit

- 3. can ripple all the way through the adder (*ripple carry adder*)

- 4. Ripple carry adders are slow since the carry propagates from a unit to the next sequentially

- Subtraction can be performed by inverting the operand and setting the "CarryIn" input for the whole adder to 1

- 6. (i.e. using two's complement)

### Summary

- Adder and multiplier circuits reflect human algorithms for addition and multiplication.

- Adders and multipliers are built hierarchically.

- We start with half adders and full adders and work our way up.

- Building these circuits from scratch using truth tables and K-maps would be pretty difficult.

- Adder circuits are limited in the number of bits that can be handled. An overflow occurs when a result exceeds this limit.

- There is a tradeoff between simple but slow ripple carry adders and more complex but faster carry lookahead adders.

- Multiplying and dividing by powers of two can be done with simple shifts.

# HARDWARE DESCRIPTION LANGUAGE

### Design of a Half Adder (halfadd)

#### Behavioural

LIBRARY ieee USE ieee.std\_logis\_1164.all

ENTITY halfadd IS

Port (A, B: INSTD\_LOGIC;sum, Cout: OUTSTD\_LOGIC);

END HA;

ARCHITECTURE behavioural OF halfadd IS BEGIN Cout <= A AND B; sum <= A XOR B; END behavioural;

### Design of Full Adder (fulladd)

### Behavioural

LIBRARY ieee ;

USE ieee.std\_logic\_1164.all;

ENTITY fulladd IS

PORT (

Cin, x, y

: IN

STD\_LOGIC ;

s, Cout

: OUT

STD\_LOGIC ) ;

END fulladd ;

```

ARCHITECTURE Behavioural OF fulladd IS

BEGIN

```

s <= x XOR y XOR Cin ; Cout <= (x AND y) OR (Cin AND x) OR (Cin AND y) ; END Behavioural ;

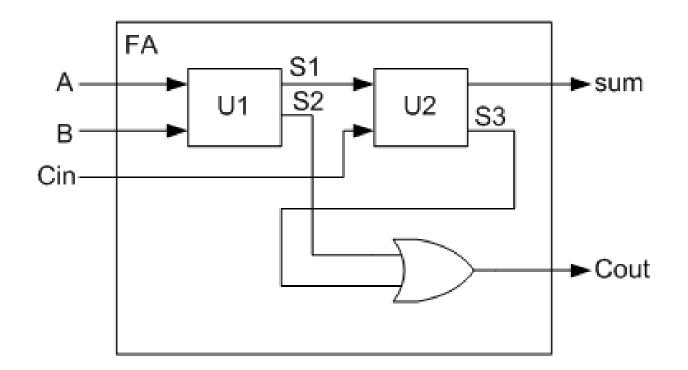

### **Design of Full Adder (FA)**

• Structural (use halfadd)

```

ENTITY FA IS

A, B, Cin : IN

PORT (

STD_LOGIC;

sum, Cout : OUT

STD_LOGIC );

END FA;

ARCHITECTURE Structural OF FA IS

signal S1, S2, S3 : STD_LOGIC;

COMPONENT halfadd

Port (

A, B

: IN

STD_LOGIC;

sum. Cout : OUT

STD LOGIC);

BEGIN

U1 : halfadd

PORTMAP ( A, B, S1, S2);

U2 : halfadd

PORTMAP (S1, Cin, Sum, S3);

```

Cout  $\leq$  S2 OR S3;

END LogicFunc;

### **Design of Full Adder (FA)**

• Structural (use halfadd)

### Design a 4-bit adder

| LIBRARY ieee ;<br>USE ieee.std_logic_1164.all ;                                                                              |                                 | ARCHITECTURE Structure OF adder4 IS<br>SIGNAL c1, c2, c3 : STD_LOGIC ;<br>COMPONENT fulladd<br>PORT ( Cin, x, y : IN                                                        |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENTITY adder4 IS                                                                                                             |                                 | STD_LOGIC ;                                                                                                                                                                 |

| PORT ( Cin<br>: IN STD_LO<br>x3, x2, x1, x0<br>STD_LOGIC ;<br>y3, y2, y1, y0<br>STD_LOGIC ;<br>s3, s2, s1, s0<br>STD_LOGIC ; | DGIC ;<br>: IN<br>: IN<br>: OUT | s, Cout : OUT<br>STD_LOGIC ) ;<br>END COMPONENT ;<br>BEGIN<br>stage0: fulladd PORT MAP ( Cin, x0, y0, s0,<br>c1 ) ;<br>stage1: fulladd PORT MAP ( c1, x1, y1, s1, c2<br>) ; |

| Cout<br>STD_LOGIC);                                                                                                          | : OUT                           | stage2: fulladd PORT MAP ( c2, x2, y2, s2, c3 ) ;                                                                                                                           |

| END adder4 ;                                                                                                                 |                                 | stage3: fulladd PORT MAP (<br>Cin => c3, Cout => Cout, x => x3, y =><br>y3, s => s3 );                                                                                      |

END Structure ;

### Design a 4-bit adder (using Package)

LIBRARY ieee ; USE ieee.std\_logic\_1164.all ; USE work.fulladd\_package.all ;

ENTITY adder4 IS

PORT (Cin

|                | : IN  | STD_LOO | GIC ;         |

|----------------|-------|---------|---------------|

| x3, x2, x1, x0 | : IN  | STD_LOO | GIC ;         |

| y3, y2, y1, y0 | : IN  | STD_LOO | GIC ;         |

| s3, s2, s1, s0 | : OUT | STD_LOO | GIC ;         |

| Cout           |       | : OUT   | STD_LOGIC ) ; |

END adder4;

ARCHITECTURE Structure OF adder4 IS SIGNAL c1, c2, c3 : STD\_LOGIC ; BEGIN stage0: fulladd PORT MAP ( Cin, x0, y0, s0, c1 ) ; stage1: fulladd PORT MAP ( c1, x1, y1, s1, c2 ) ; stage2: fulladd PORT MAP ( c2, x2, y2, s2, c3 ) ; stage3: fulladd PORT MAP ( Cin => c3, Cout => Cout, x => x3, y => y3, s => s3 ) ; END Structure ;

### Design a 4-bit adder

• Fulladd package

LIBRARY ieee ; USE ieee.std\_logic\_1164.all ;

PACKAGE fulladd\_package IS COMPONENT fulladd PORT ( Cin, x, y : IN STD\_LOGIC ; s, Cout : OUT STD\_LOGIC ) ; END COMPONENT ; END fulladd\_package ;

NurulHazlina/BEE2243/A.Circuit

## **Designing ALU**

• Functionality ALU

|           | Inputs | Outputs |

|-----------|--------|---------|

| Operation | S2S1S0 | F       |

| Clear     | 000    | 0000    |

| B-A       | 001    | B – A   |

| A – B     | 010    | A – B   |

| ADD       | 011    | A + B   |

| XOR       | 100    | A XOR B |

| OR        | 101    | A OR B  |

| AND       | 110    | A AND B |

| Preset    | 111    | 1111    |

### **Designing ALU**

LIBRARY ieee ; USE ieee.std\_logic\_1164.all ; USE ieee.std\_logic\_unsigned.all ;

ENTITY alu IS PORT (s : IN STD\_LOGIC\_VECTOR(2 DOWNTO 0) ;

A, B : IN STD\_LOGIC\_VECTOR(3 DOWNTO 0) ;

F : OUT STD\_LOGIC\_VECTOR(3 DOWNTO 0) ) ;

END alu ;

ARCHITECTURE Behavior OF alu IS BEGIN

PROCESS ( s, A, B ) BEGIN CASE s IS

WHEN "000" => <= "0000" : WHEN "001" => F <= B - A : WHEN "010" => F <= A - B : WHEN "011" => F <= A + B : WHEN "100" =>  $F \leq A XOR B$ ; WHEN "101" =>  $F \leq A OR B$ : WHEN "110" =>  $F \leq A AND B$ : WHEN OTHERS => F <= "1111" ; END CASE : END PROCESS : END Behavior :