# Chapter 5: Project Planning and Designing Tools

Credit to : Dr. MD Rizal Othman Faculty of Electrical & Electronics Engineering Universiti Malaysia Pahang

Ext: 6036

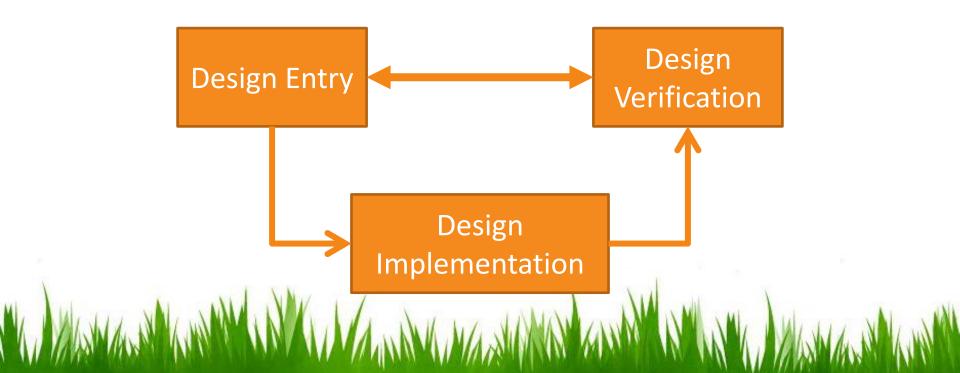

- Design Entry

- Create design :- Schematic or HDL

- Design Implementation

- Partition

- Place

create bit stream file

- Route

- Design Verification

- Use simulator to check functionality

- Check operation after loading

• Design Entry

– Create design :- Schematic or HDL

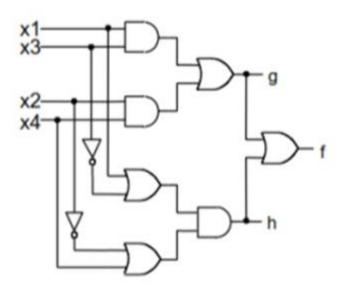

#### // Example 4

module example4 (x1, x2, x3, x4, f, g, h); input x1, x2, x3, x4; output f, g, h;

assign g = (x1 & x3) | (x2 & x4);assign h =  $(x1 | \sim x3) \& (\sim x2 | x4);$ assign f = g | h;

endmodule

#### **FPGA Generic Design Flow**

- Design Implementation

- Implementing HDL to FPGA (something that fpga can use)

- 1. Partition

- 2. Place

- 3. Route

- Design Verification

- Use simulator to check functionality

- Check operation after loading

## Types of verification

- Simulation

- simulate the HDL code with no timing information

- simulate the synthesized with no timing information

- Static timing analysis (STA)

- Compares the implemented design to specified timing constrains

### Verification Plan

- Bench Testing

- Test a physical system (prototype) in a controlled environment (lab)

- Field testing

- Test the final product in a real-world environment

- Combinational Logic must be covered by 4input and 1-output "gate" – done in translation process.

- FF from the circuit must map to FPGA FF.

- Placement in general attempts at wiring minimization.

- − Wiring increases → delay increase → speed decreases

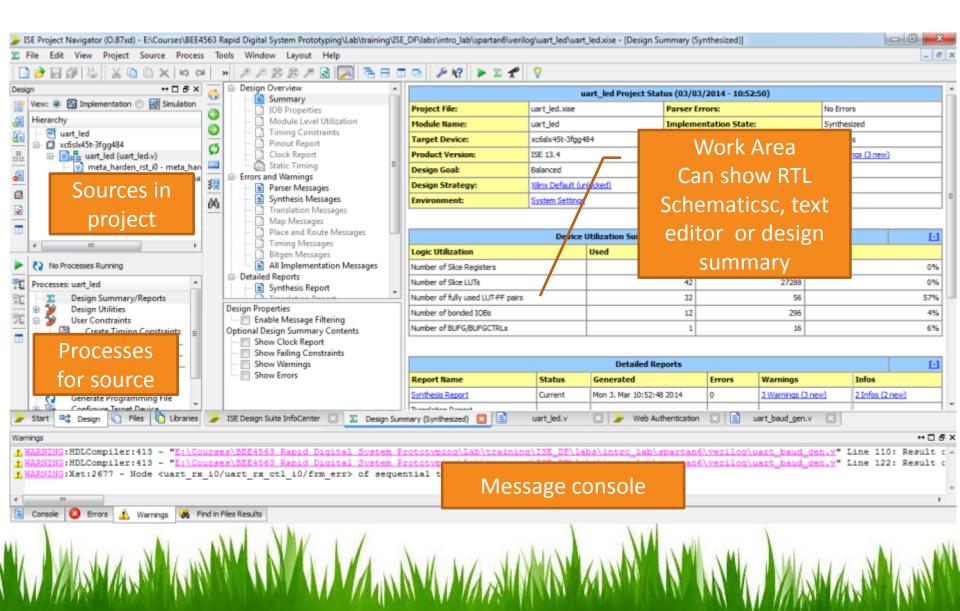

#### Introduction to Xilinx ISE

- Tool to configure FPGA provided by Xilinx

- Integrated Software Environment

- Integrated collection of tools with GUI (user friendly). Eg: XST, PACE, CoreGen, Constraint Editor, Impact

- Support all the steps required to complete the design

- 1. Design Entry

- .sch, .v , .vhd

- 2. Synthesis : use XST (Xilinx Synthesis Tool)

- Produces a netlist file starting from an HDL/Schematic description

- Converts .sch, .v , .vhd  $\rightarrow$  .ngc (netlist file)

- 3. Translate : NGD Build

- Reads all input design netlists and then write the results in a single merged file, that describes logic circuit constrains.

### Xilinx development flow

- 3. Translate : NGD Build

- NGD is Native Generic Database: describes the logic design reduced to xilinx primitives

- 4. Mapping

- Maps the logic on device components

- Takes the netlist and group the logical element into CLBs and IOBs

- Generate NCD and PCF

- NCD (Native Circuit Description)

- Represents the physical circuit description of the input design as applied to a specific device → device dependent

### Xilinx development flow

#### 5. Place and Route

- Determines the placement of the cells and the routing between the cells

- PCF (Physical Constrains File)

- Contains physical constrains

- Info about which CLB can be used and which CLB cannot be used (increase delay)

- 6. Bit Stream Generation

- A bit stream is a stream of data that contains the location information for logic on a device

- 7. Configuration/Programming

- Download a bit file into FPGA using JTAG port

HDL compiler → XST Simulator → Xilinx ISEsim Core Generator & Arch. Wizard → CoreGen Pinout and Area Constrain Editor → PACE Implementation → Translate/MAP/P&R Device Configuration → IMPACT

#### **Project Navigator**

# □ ISE<sup>®</sup> Design Suite

- Integrated Synthesis Environment

- Project Navigator

- □ChipScope<sup>™</sup> Pro Tool

- Embedded Development Kit

- □ WebPACK<sup>™</sup> software

#### Xilinx Design Process

- Step 1: Design Entry

- HDL (Verilog or VHDL)

- Step 2: Synthesis

- Translate HDL files into a netlist

- Step 3: Implementation

- Translate, Map, Place & Route

- Step 4: Configuration

- Simulation can occur after Steps 1, 2, or 3

#### Xilinx Design Process

- Step 1: Design Entry

- HDL (Verilog or VHDL)

- Step 2: Synthesis

- Translate HDL files into a netlist

- Step 3: Implementation

- Translate, Map, Place & Route

- Step 4: Configuration

- Simulation can occur after Steps 1, 2, or 3

#### **Tool and Processes**

View Project Source Process 🗵 File Edit Tools Window Layout Help 🗋 彦 🗟 🎼 🌭 Ж 50 B G. » 2 Design Overview ⇔□₽× Desian Summary View: 💿 🙀 Implementation 🔘 🌆 Simulation **IOB** Propertie æ Hierarchy Module Level Θ Timing Const 🖻 uart led Pinout Report in Marchely45t-3faa484 Ç ₹. 111 ¥ Clock Report HTHL Static Timing No Processes Running Errors and Warnings 30 E Parser Messac ₽t Processes: uart led E Synthesis Me A Ľ, Design Summary/Reports Translation M **Design Utilities** ÷ Map Message ЯĽ ė User Constraints Place and Rou Create Timing Constraints Timing Messa **Design entry** I/O Pin Planning (PlanAhead) - Pre-Synthesis Bitgen Messa I/O Pin Planning (PlanAhead) - Post-Synthesis E All Implemen Floorplan Area/IO/Logic (PlanAhead) Detailed Reports 🖨 🏹 Synthesize - XST Synthesis Rep **∎** View RTL Schematic N N N Translation Re **Synthesis** View Technology Schematic Map Report  $\overline{\mathbf{O}}$ Check Syntax C 5 Generate Post-Synthesis Simulation Model Design Properties Implement Design Enable Message F 3 ( **5** ) Translate Optional Design Summar ÷... Implementation Show Clock Repo 🗄 - 🔁 Map Show Failing Con Place & Route Ē~ 🔁 Generate Programming File Show Warnings C) **Configure Target Device** Show Errors Configuration Generate Target PROM/ACE File Manage Configuration Project (iMPACT) Additional Tool Analyze Design Using ChipScope <u>е</u>н Design Files Libraries Start ISE Design Suite InfoCente Warnings WARNING: HDLCompiler: 413 - "E:\Courses\BEE4563 Rapid Digital System ING:HDLCompiler:413 - "E:\Courses\BEE4563 Rapid Digital System <u>VARNING</u>:Xst:2677 - Node <uart rx i0/uart rx ctl i0/frm err> of seque

ISE Project Navigator (0.87xd) - E:\Courses\BEE4563 Rapid Digital System Prototyping\Lab\training\IS