# Introduction to HDL - TestBench

Credit to: Dr. MD Rizal Othman

Faculty of Electrical & Electronics Engineering

Universiti Malaysia Pahang

Ext: 6036

#### Overview

- We have concentrated on Verilog for synthesis

- Can also use Verilog as a test language

- Very important to conduct comprehensive verification on your design

- To simulate your design you need to produce an additional module that includes your synthesizable Verilog design.

- Usually referred to as a TEST BENCH or TEST FIXTURE

- Not hardware, just additional Verilog!

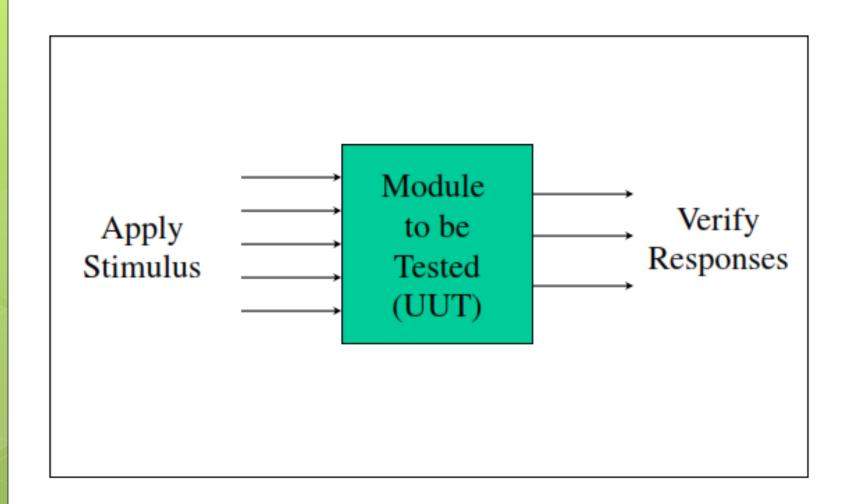

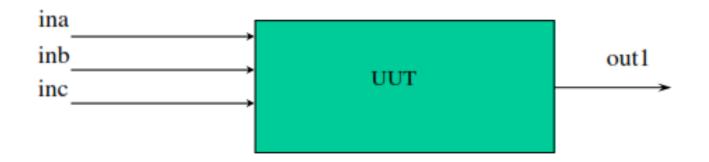

#### Test Bench

- A virtual platform containing the design to be tested (UUT) and virtual wires connected to the UUT inputs and outputs.

- To exercise and verify the correctness of a design to be implemented in hardware

- Has three main purposes

- to generate stimulus for simulation

- to apply this stimulus to the module under test and to collect output responses

- to compare output responses with expected values

- Test Bench should be created by a different engineer than the one who created the synthesizable Verilog

## Test Bench – Virtual Platform

#### **Test Bench Overview**

- A Test Bench module consists of

- Port list has NO ports

- Instantiate module to be tested (UUT)

- Declare internal signals to wire to UUT inputs and outputs

- Verilog statements to provide stimulus and verify UUT responses

- Designing a test bench that has good coverage can be a very involved project!

## Test Bench - general structure

```

module decoder_tf;

internal signal declarations

UUT: test_component instantiation

signals to generate stimulus

statements to verify responses

endmodule

```

## Example Decoder – is the design correct?

```

X

ISE Text Editor (P.15xf) - [decoder.v]

- 5 X

File Edit View Window Layout Help

module decoder (

22

23

input

[2:0] sw,

output reg [7:0] led

24

25

);

26

always @ (sw)

case (sw)

29

0: led = 8'b00000001;

30

1: led = 8'b00000010;

31

2: led = 8'b00000100;

32

3: led = 8'b00011000; // mistake

33

4: led = 8'b00010000;

34

5: led = 8'b00100000:

35

6: led = 8'b01000000;

7: led = 8'b10000000;

37

endcase

38

endmodule

← III.

decoder.v

```

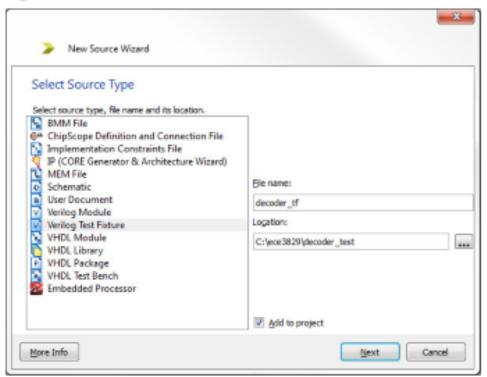

#### Create Test Fixture

- Select Simulation View

- Select Project => New Source

Select decoder source to associate with test fixture

## Outline of Test Fixture produced

```

0 E

SE Text Editor (P.15xf) - [decoder_tf.v]

Edit View Window Layout Help

- 8 X

'timescale ins / ips

// Comments deleted

module decoder tf;

// Inputs

reg [2:0] sw;

// Outputs

wire [7:0] led;

11

13

// Instantiate the Unit Under Test (UUT)

decoder uut (

. sw (sw) ,

.led(led)

12

17

18

initial begin

19

// Initialize Inputs

20

sw = 0:

22

// Wait 100 ns for global reset to finish

23

#100:

24

25

// Add stimulus here

26

end

29

endmodule

31

decoder_tf.v

```

## Apply input stimulus

```

0

ISE Text Editor (P.15xf) - [decoder_tf.v]

_ E X

File Edit View Window Layout Help

22

// Wait 100 ns for global reset to finish

23

#100;

24

25

sw = 3'b001: // check all input combinations

26

27

#100;

28

sw = 3'b010;

#100;

29

sw = 3'b011:

30

31

#100;

sw = 3'b100;

32

33

#100:

34

sw = 3'b101;

35

#100;

sw = 3'b110;

36

37

#100:

38

sw = 3'b111;

#100;

39

40

41

end

42

endmodule

43

44

decoder_tf.v

```

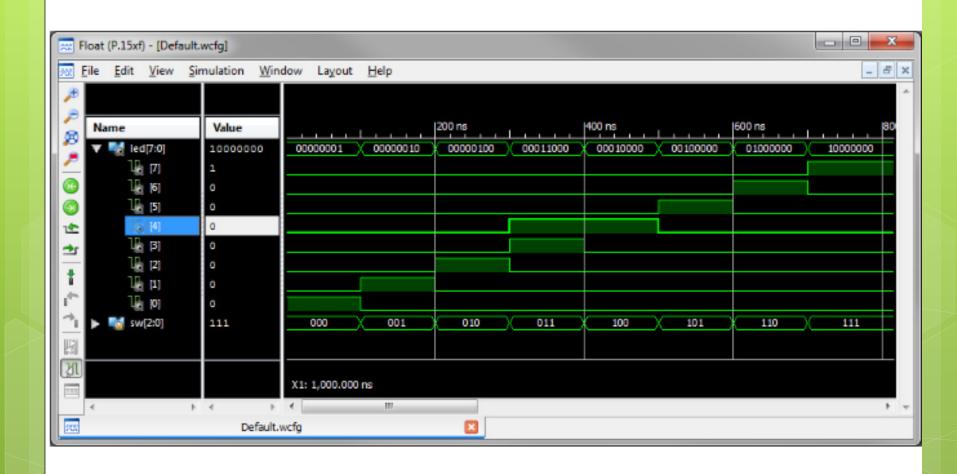

#### Simulate Behavioral Model

### Testing sequential logic

Creating clock signal

```

00

ISE Text Editor (P.15xf) - [decoder tf.v]

- 5 X

File Edit View Window Layout Help

4≣

wire [7:0] led;

11

12

13

// Instantiate the Unit Under Test (UUT)

decoder uut (

14

. sw (sw),

.led(led)

16

);

17

Window

Layout

18

reg clk 50M;

19

20

// create 50MHz clock

always

21

22

begin

0000

00000001

00000010

00000100

23

clk 50M = 0;

// 10 times time units = 10ns

24

#10:

clk 50M = 1;

#10:

26

end

28

X1: 1,000.000 ns

initial begin

29

decoder_tf.v

```

Can also 'restart', 'run', and add internal signals to wave

## Discussion 1

Testbench 4 bit ALU